| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | |

| 7 | 8 | 9 | 10 | 11 | 12 | 13 |

| 14 | 15 | 16 | 17 | 18 | 19 | 20 |

| 21 | 22 | 23 | 24 | 25 | 26 | 27 |

| 28 | 29 | 30 | 31 |

- devops

- OpenSource

- Spring

- 파이썬

- java

- DI

- 하이브리드 데이터 모델

- elastic search

- 메소드

- curl

- umc

- jwt-java

- kong

- mybatis

- Nice

- 자료구조

- prometeus

- fosslight

- pyannote

- monitoring

- docker

- 화자분리

- API Gateway

- template/callback

- ELK

- supabase

- metricbeat

- konga

- C++

- roll over

- Today

- Total

youngseo's TECH blog

컴퓨터 구조론 본문

컴퓨터 기본 구성

사용자

응용 소프트웨어

시스템 소프트웨어 (ex. 운영체제, Device Driver, Compiler, Interpreter, linker분할, loader적재)

하드웨어

컴퓨터 주요 기능

(입출력, 기억, 제어, 연산, 통제)

(프로그램 실행, 데이터 저장, 데이터 이동, 입출력, 제어)

SOFTWARE

하드웨어의 동작을 지시하고 제어하는 역할을 하는 역할을 하는 명령어들의 집합인 프로그램과 프로그램에 필요한 데이터 통칭

-컴퓨터가 일을 처리하기 위해 컴퓨터가 이해할 수 있는 언어로 작성한 명령어들의 집합

-프로그램+데이터+관련 문서

-시스템 소프트웨어

-응용 소프트웨어

HARDWARE

-정보/데이터의 전송 및 처리가 실제 일어나는 물리적인 실체

컴퓨터 시스템의 개념적 구성요소

HW의 기본 구성요소

1. 중앙처리장치(CPU, Processor)

컴퓨터 시스템에 부착된 모든 장치의 동작을 제어하고 명령을 실행

제어장치+연산장치(ALU)+레지스터+CPU 내부버스 -> Fetch+Execution

2. 기억장치(Memory) --주로 RAM

RAM?

-CPU가 처리할 프로그램과 데이터를 일시적으로 저장

-반도체 기억장치 칩들로 구성

-메인메모리-- 메인 메모리에 올라와있는 명령어를 CPU가 수행한다.

-가격이 높고, 저장할 때 면적을 많이 차지 --그래서 보조기억장치를 장착함.

-Random Access Memory 고속 엑세스 가능, Volatile Memory 일시적 저장만 가능

ROM?

-데이터를 읽을 수만 있는 비휘발성 메모리

-전원이 꺼져도 기록된 내용이 보관됨

-Booting : 롬에 부트로더, 램에 운영체제OS를 올린다.

3. 보조기억 장치

-저장 밀도가 높고 비트당 가격이 낮음

-영구 저장 가능

-종류 ---하드디스크, 플래시 메모리, CD-ROM

4. 입출력장치

-사용자와 컴퓨터 간 대화를 위함

-유무선 통신 네트워크 인터페이스 장치

5. 시스템 버스

-CPU와 시스템 내의 다른 요소들 사이에 정보 교환 통로

주소버스 - 주소선은 CPU와 접속될 수 있는 최대 기억장치 용량 결정

데이터버스 - 데이터 선은 CPU가 한 번에 전송할 수 있는 비트 수 결정

제어버스 - CPU가 시스템 내의 각종 요소들의 동작 제어를 위한 신호 선들의 집(쓰기 신호, 읽기 신호)

프로그램 코드

-고급 언어 (C, C++, PASCAL, FORTRAN)

컴파일러, 어셈블러 등을 이용해 기계어로 번역

-어셈블리 언어

Interpreter. 기계어와 일대일 대응시킴

가짜 예시 ADD R1 R2 / LDA 5 : 5를 누산기에 적재

-기계어

01010111101011 이런 느낌

[참고]C 프로그램의 컴파일 단계??

- Processing -C에서 명령어 실행시킴

- Compilation -컴파일러는 원본 소스 코드에서 구문 오류에 대한 확인을 위해 조사

- Assemble - 모든 명령어를 이진코드로 변환

- Linking - 실행 프로그램은 프로그래머 요청 이후 CPU가 실행 시도

컴퓨터 발전(역사)

-파스칼 계산기 : 덧셈+뺄셈

-Leibniz 의 기계 : +, -, x, %

-Charles Babbage의 미분기관 - 덧셈 뺄셈

-Charles Babbage의 해석기관 - 모든 수학 연산 가능, 프로그래밍 가능(Ada Lovelace), 수의 부호 검사를 이용한 조건 분기, 제어 카드를 이용한 실행 순서 변경 등 가능

-Turing machine - 기계적 방식으로 모든 수학 문제를 해결할 수 없다는 것을 가상기계로 증명

-Church-Turing thesis - 컴퓨터알고리즘으로 할 수 있는 모든 일은 튜링 기계로 실행 가능하다.

-폰 노이먼 아키텍처 (IAS 컴퓨터)

이전은 ENIAC (Hardwired Program Computer)

프로그램 내장형 컴퓨터. 프로그램과 데이터를 주기억장치에 기억시켰다.

앨런튜링 모델을 기계화한 형태

컴퓨터의 세대별 발전

0 기계적 릴레이 금속 기어, 카드

1 진공관 자기 드럼 하드웨어 개발에 중점. 부피 크고 전력 소모 많음

2 트랜지스터 고급 언어 등장

3 SSI, MSI RAM, ROM OS 개발, 다중 프로그래밍, 고급 언어 활용

4 LSI, VLSI SRAM, DRAM 객체지향언어 사용, 개인용 컴퓨터, 병렬 처리 기능 강화

5 VLSI, ULSI, GLSI, SoC SRAM, DRAM, flash 노이만 구조 추구, 멀티코어 사용, 유비쿼터스 컴퓨팅

컴퓨터 성능

성능 = 1/CPU 실행시간

응답시간 = 하나의 프로그램을 처리하는 데 소요되는 시간

-암달의 법칙

-명령어 개수 C

C*명령어당 평균 시간 or sum(Ck * Ck 하나의 실행시간)

-clock 속도(rate) : Hz, 0과 1 신호가 한 번씩 실행되는 주기 수 = 1/clock cycle

-CPU실행시간 = C * 명령어당 평균 시간 * clock cycle = C * 명령어당 평균 시간 / clock rate

성능 관련요소에 영향을 미치는 요인들 --생각해보쟈. 우리가 공부하는 이유일 수 있음

-실행되는 명령어 개수는 알고리즘과 명령어 집합 구조에 영향 받음

-평균 CPI 성능은 알고리즘, 명령어 집합 구조(단순한 명령어)와 컴퓨터 구성(CPU내 연산 병렬화)에 영향받음

-클럭 사이클 시간은 명령어 집합구조, 컴퓨터 구성 및 개발 수준(더 빠른 회로기술, 패키징 밀도 높이기)에 영향 받음

벤치마크와 성능 평가 척도

벤치마크 - 성능을 평가하기 위해서 작업 부하로 선택된 프로그램의 모음

평가척도 : MIPS, MFLOPS 등

MIPS : 클록속도 / CPI * 10**6

MFLOPS = 부동소수점 연산 개수 / 실행시간 * 10**6

컴퓨터 종류

개인용 컴퓨터 - pc, 노트북

임베디드 컴퓨터 - 특징:실시간 처리/최소의 비용으로 필요한 만큼의 성능 제공

중형급 컴퓨터 시스템

- 워크스테이션(개인용 컴퓨터 규모에 미니컴퓨터 성능 집약시킨 고성능 컴퓨터)

OS가 UNIX/LINUX. 3차원 동영상처리, 시뮬레이션 등 가능

- 슈퍼미니컴퓨터

다중프로세서 구조(20~30개) . OS가 UNIX.

메인프레임 컴퓨터

-중앙집중식 컴퓨팅을 위한 대형 컴퓨터. 동시에 많은 사용자를 위한 강력한 처리 기능 가짐.

-시분할(모든 사용자 사이의 시분할)

슈퍼컴퓨터

-VSLI 회로 설계, 항공우주공학, 천문학, 인공지능 …

현대 컴퓨터의 주요 부품들

진공관 ---- 트랜지스터(제2세대) ----- 집적 회로 IC (제3세대) ----LSI, VLSI(4세대)

IC장점 - 전기적 통로가 짧아져 동작 속도 상승 / 컴퓨터 크기 감소 / 부품 기능의 신뢰도 향상 / 전력 감소

Cpu 구성요소

*ALU

*제어장치

*레지스터

ISA(명령어 집합 구조)

구조 설계 시 고려되어야 하는 것 : 명령어 형식-opcode 길이 ?? / 주소지정 방식 / 연산 종류-전송,처리,제어,입출력 / 데이터 타입-데이터 길이.?비트 수 등

CYCLE

인출 사이클 : CPU가 기억장치로부터 명령어 읽어오는 단계

MAR<-PC

MBR <-M[MAR], PC<-PC+1

IR<-MBR

실행 사이클 : 명령어를 해독하고 실행하는 단계

전송, 처리, 제어, 입력

사이클에서의 호출/복귀

인출사이클은 똑같음 : IR <-M[PC]; PC<-PC+1

실행사이클

-호출 : TOS<-PC ; PC<-proc

-복귀 : PC<-TOS

가상 컴퓨터 명령어

LDA 적재 - 1

ADD - 3

STA - 2

JMP - 5

조건분기 명령어

S(STATUS)- 0 1

C(CARRY) - 올림수가 있으면 1, 없으면 0

V(OVERFLOW) - 오버플로우가 있냐

S/N - 양수 / 음수

Z - 연산결과 0 이냐

DATA TRAFFIC

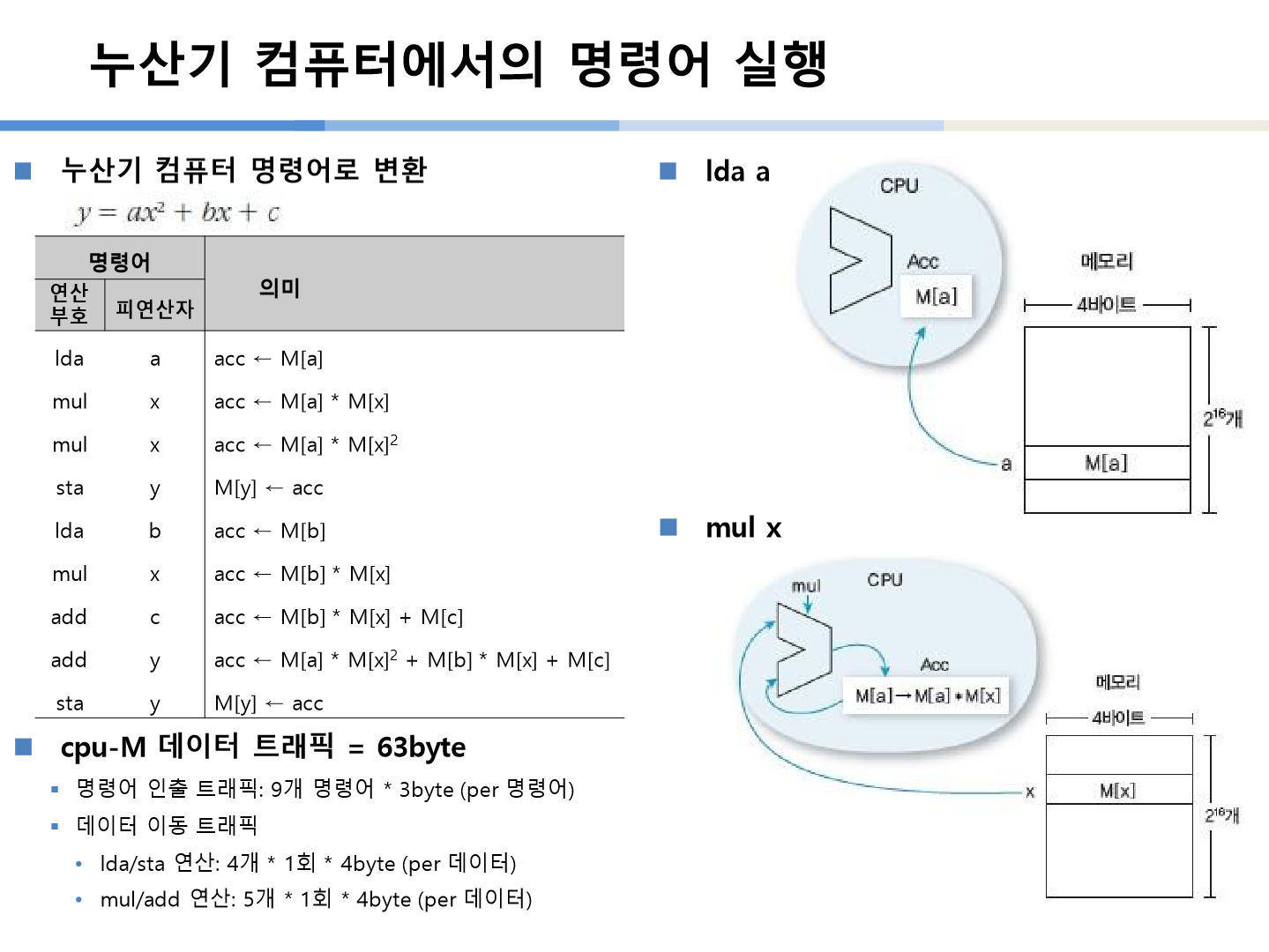

폰노이먼(cpu-memory 분리) M-M 컴퓨터 / 스택 컴퓨터 (CPU-M 컴퓨터 ) / 누산기 컴퓨터 / 범용 레지스터 컴퓨터

-폰노이먼 : 한 명령어당 2회 이동하는 게 너무 크다.

주어지는 조건 : 연산부호 크기 8비트(1바이트), 연산마다 최대 2개의 피연산자 사용, 메모리 주소 2바이트, 데이터 크기 4바이트

이때,

명령어 인출 트래픽 : 5(연산부호 1바이트+피연산주소1 2바이트+피연산주소2 2바이트)*7 (mov,mul,add,y,a,b,c) = 35

데이터 이동 트래픽 : mov : 2(2회 이동)*4바이트*2개 = 16

mul, add : 3(개 - a,b, 결과데이터)*4바이트*5개 (명령어 개수) = 60

총 111

이래서 CPU에 기억장치 필요

-데이터 트래픽 감소

-반복적으로 사용되는 피연산자를 CPU 내부 기억장치에 보관.

-메모리 재참조 필요성 제거

-명령어 트래픽 감소

-스택컴퓨터 / CPU - M -0주소 명령어

-일단 2개의 명령어 종류에 따라 다른 크기

이 때,

명령어 인출 트래픽

Push/pop : 7개 * 3(연산부호 1바이트 +피연산자 2 바이트)

Mul / add : 5개 * 1(연산부호 1바이트)

데이터 이동 트래픽

Push/pop : 4바이트 * 1(이동 횟수, 메모리에서 가져오는 거 한 번만 하니까)

Mul/add : 4바이트 * 0(이동횟수, 메모리에 가는 일 없음)

총 54

-ACC -1주소 명령어

LDA 든, MUL이든 메모리를 참조하긴 함.

-범용 레지스터 - 2주소 명령어, 레지스터 16개 사용

명령어 인출 트래픽

-load/store : 5(개)* 4(바이트)

-mul/add : 5(개)*2(바이트)

데이터 이동 트래픽

-load/store : 5(개수)*4(데이터 트래픽)

-mul/add : 5*(0)

총 50

주소 지정 방식

왜?? - 제한된 수의 명령어 비트를 이용하여 사용자가 여러가지 방법으로 오퍼랜드의 주소를 결정하도록 해주며, 더 큰 용량의 기억장치를 사용할 수 있도록 하기 위함

0단계

-즉시 주소지정 방식

-묵시적 주소지정 방식

1단계

-레지스터 주소지정 방식 EA=R

-직접 주소지정 방식 EA = A

2단계

-레지스터 간접 주소지정 방식 EA=Reg[x]

-메모리 간접 주소지정 방식 EA=Mem[x]

-변위 주소지정 방식

=베이스-레지스터 주소지정 방식 EA=Reg[x]+A

=PC 상대 주소지정 방식 EA=Reg[x]+A

CISC / RISC

왜 데이터 2의 보수로 쓰는가?

-부호-크기 방식 : 두 숫자의 부호에 따라 연산 방법이 다름

-1의 보수: 부호와 상관없이 연산하지만 순환자리 올림 발생

-2의 보수

실수형 표현

부호비트 | 지수 필드 | 가수 필드

5.625를 실수형으로 표현해보자. 고정소수점 표현 방식으로 하면 101.101 -> 1.01101 * 2^2

가수부는 01101(맨 앞 1은 당연하므로 생략), 지수부는 2(이 때 지수부도 양/음 값 판별 해줘야 함)

정리하면 10진수 101.101은 0 | 1000 0001 | 011 0100 0000 0000 0000 0000이 된다.

비수치 데이터

BCD - 7(1-패리티 비트, 2-존비트, 4-숫자비트)

ASCII - 알파벳을 사용하는 .

유니코드 - 다양한 문자 표현

항공대학교 길현영 교수님 컴퓨터 구조론 수업을 바탕으로 정리한 글입니다.

'KAU' 카테고리의 다른 글

| [KOTLIN] 객체지향 프로그래밍 문법 정리 (0) | 2022.12.12 |

|---|---|

| 데이터베이스 (3) | 2022.10.23 |

| 개발 블로그 시작 (0) | 2022.05.21 |